扩散阻挡层用于防止金属杂质(如Cu、Al)向硅基体扩散,典型材料包括氮化钛(TiN)、氮化钽(TaN)和碳化钨(WC)。管式炉在阻挡层沉积中采用LPCVD或ALD(原子层沉积)技术,例如TiN的ALD工艺参数为温度300℃,前驱体为四氯化钛(TiCl₄)和氨气(NH₃),沉积速率0.1-0.2nm/循环,可精确控制厚度至1-5nm。阻挡层的性能验证包括:①扩散测试(在800℃下退火1小时,检测金属穿透深度<5nm);②附着力测试(划格法>4B);③电学测试(电阻率<200μΩ・cm)。对于先进节点(<28nm),采用多层复合阻挡层(如TaN/TiN)可将阻挡能力提升3倍以上,同时降低接触电阻。管式炉适用于晶圆退火、氧化等工艺,提升半导体质量,欢迎咨询!无锡一体化管式炉退火炉

晶圆预处理是管式炉工艺成功的基础,包括清洗、干燥和表面活化。清洗步骤采用SC1(NH₄OH:H₂O₂:H₂O=1:1:5)去除颗粒(>0.1μm),SC2(HCl:H₂O₂:H₂O=1:1:6)去除金属离子(浓度<1ppb),随后用兆声波(200-800kHz)强化清洗效果。干燥环节采用异丙醇(IPA)蒸汽干燥或氮气吹扫,确保晶圆表面无水印残留。表面活化工艺根据后续步骤选择:①热氧化前在HF溶液中浸泡(5%浓度,30秒)去除自然氧化层,形成氢终止表面;②外延生长前在800℃下用氢气刻蚀(H₂流量500sccm)10分钟,消除衬底表面微粗糙度(Ra<0.1nm)。预处理后的晶圆需在1小时内进入管式炉,避免二次污染。无锡制造管式炉SiN工艺管式炉通过先进控温系统实现锂电材料精确控温。

半导体制造中的扩散工艺离不开管式炉的支持。当需要对硅片进行掺杂以改变其电学性能时,管式炉可营造合适的高温环境。将含有特定杂质(如磷、硼等掺杂剂)的源物质与硅片一同置于管式炉中,在高温作用下,杂质原子获得足够能量,克服晶格阻力,逐渐向硅片内部扩散。管式炉均匀的温度场分布保证了杂质在硅片内扩散的一致性,使得硅片不同区域的电学性能趋于均匀。通过精确调节管式炉的温度、扩散时间以及炉内气氛,能够精确控制杂质的扩散深度和浓度分布,满足不同半导体器件对于电学性能的多样化需求,进而提升半导体器件的性能和可靠性。

在半导体CVD工艺中,管式炉通过热分解或化学反应在衬底表面沉积薄膜。例如,生长二氧化硅(SiO₂)绝缘层时,炉内通入硅烷(SiH₄)和氧气,在900°C下反应生成均匀薄膜。管式炉的线性温度梯度设计可优化气体流动,减少湍流导致的膜厚不均。此外,通过调节气体流量比(如TEOS/O₂),可控制薄膜的介电常数和应力。行业趋势显示,低压CVD(LPCVD)管式炉正逐步兼容更大尺寸晶圆(8英寸至12英寸),并集成原位监测模块(如激光干涉仪)以提升良率。

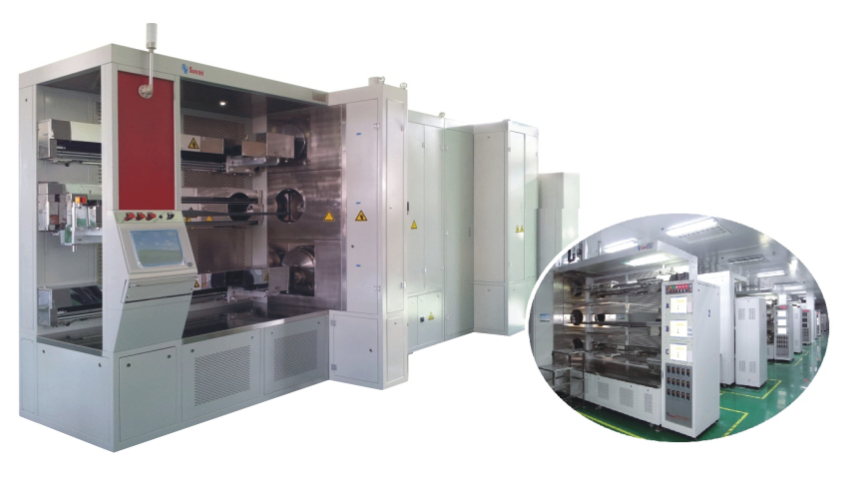

管式炉在碳化硅(SiC)和氮化镓(GaN)制造中面临高温(1500℃以上)和强腐蚀气氛(如HCl)的挑战。以SiC外延为例,需采用石墨加热元件和碳化硅涂层石英管,耐受1600℃高温和HCl气体腐蚀。工艺参数为:温度1500℃-1600℃,压力50-100Torr,硅源为硅烷(SiH₄),碳源为丙烷(C₃H₈),生长速率1-2μm/h。对于GaN基LED制造,管式炉需在1050℃下进行p型掺杂(Mg源为Cp₂Mg),并通过氨气(NH₃)流量控制(500-2000sccm)实现载流子浓度(10¹⁹cm⁻³)的精确调控。采用远程等离子体源(RPS)可将Mg***效率提升至90%以上,相比传统退火工艺明显降低能耗。采用先进隔热材料,减少热量损失,提升设备性能,点击咨询!无锡8英寸管式炉低压化学气相沉积系统

优化气体流速确保管式炉工艺高效。无锡一体化管式炉退火炉

管式炉在氧化扩散、薄膜沉积等关键工艺中,需要实现纳米级精度的温度控制。通过采用新型的温度控制算法和更先进的温度传感器,管式炉能够将温度精度提升至 ±0.1℃甚至更高,从而确保在这些先进工艺中,半导体材料的性能能够得到精确控制,避免因温度波动导致的器件性能偏差。此外,在一些先进的半导体制造工艺中,还对升温降温速率有着严格要求,管式炉通过优化加热和冷却系统,能够实现快速的升温降温,提高生产效率的同时,满足先进工艺对温度变化曲线的特殊需求,为先进半导体工艺的发展提供了可靠的设备保障。无锡一体化管式炉退火炉

赛瑞达智能电子装备(无锡)有限公司免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的商铺,信息的真实性、准确性和合法性由该信息的来源商铺所属企业完全负责。本站对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

友情提醒: 建议您在购买相关产品前务必确认资质及产品质量,过低的价格有可能是虚假信息,请谨慎对待,谨防上当受骗。